# Intel<sup>®</sup> 82576EB Gigabit Ethernet Controller Specification Update

LAN Access Division (LAD)

Revision 2.85 September 2012

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.htm.

Intel and Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\* Other names and brands may be claimed as the property of others.

Copyright © 2008, 2009, 2010, 2011, 2012; Intel Corporation. All Rights Reserved.

# Revisions

| Date           | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|----------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| January 2008   | 1.0      | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| January 2008   | 1.1      | Internal work copy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| March 2008     | 1.2      | Updated to to show additional errata and errata addressed by A1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| March 2008     | 1.3      | Internal work copy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| May 2008       | 1.9      | Updated for Production stepping. Removed information that does not apply to the production stepping removed errata fixed by documentation, mature silicon.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| July 2008      | 2.0      | Resolved documentation issues were removed. Intel Confidential stamp removed; prepared for release on Developer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| February 2009  | 2.2      | <ul><li>Non-security product information provided:</li><li>1.20 Product Code and Device Identification .</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| May 15, 2009   | 2.3      | Spec clarification added:<br>• 3. PCIe: Completion Timeout Mechanism Compliance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| August 6, 2009 | 2.4      | <ul> <li>3. PCIe: Completion Timeout Mechanism Compliance</li> <li>Errata updated or added:         <ul> <li>6. Critical Session (Keep PHY Link Up) Mode Does Not Block All PHY Resets Caused by PCIe Resets</li> <li>18. JTAG: Instruction Register Functionality Doesn't Meet IEEE Std 1149-1-2001</li> <li>20. PCIe Elastic Buffer Noise Immunity Is Not Optimized</li> <li>21. PCIe: Missing Replay Due to Recovery During TLP Transmission</li> <li>22. PCIe: LTSSM Moves from L0 to Recovery Only When Receiving TS1/TS2 on All Lanes</li> <li>24. PCIe: Missing Completion on D3 to D0 Transition</li> <li>25. PCIe: Completion Timeout Settings Not Loaded from EEPROM to GCR</li> <li>26. MSI-X: Descriptor Write-back Not Triggered by EITR Expiration in MSI-X Mode</li> </ul> </li> </ul>                                                                              |  |  |

| March 5, 2010  | 2.5      | <ul> <li>Errata updated or added.</li> <li>19. LED Stays On When SerDes Is Powered Down</li> <li>27. Tx Packet Lost After PHY Speed Change Using Auto-Negotiation</li> <li>28. PCIe: Wrong Byte Enable Bit Used for Completion Timeout Disable Bit in Device Control 2 Register</li> <li>29. PCIe: Completion with UR/CA Status Causes Unexpected Completion and Completion Timeout Errors to be Reported</li> <li>30. PCIe Hot Reset Can Lead to a Firmware Hang</li> <li>31. MACSec: Replay Protect Not Working In Check Mode</li> <li>32. MACSec: Packets With E=0, C=1 Should Not Be Handled as a Authenticated MACSec Packet</li> <li>33. MACSec: SA Creation Doesn't Clear Frame Verification Statistics</li> <li>35. MACSec: USECRXNUSA and LSECRXUNSA Statistic Counters Not Provided</li> <li>36. MACSec: When MC Is MACSec owner, MAC Reset Still Clears Keys</li> </ul> |  |  |

| March 8, 2010  | 2.6      | 36. MACSec: When MC Is MACSec owner, MAC Reset Still Clears Keys -<br>Additional information added; editorial changes made for clarity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| March 26, 2010 | 2.7      | <ul><li>Specification clarification added:</li><li>4. PCIe: Receiver Dtection Circuit Design and Established Link Width</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| June 11, 2010  | 2.71     | LinkSec references changed to MACSec.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Date               | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| August 11, 2010    | 2.72     | <ul> <li>Spec Clarifications added:</li> <li>5. Use of Wake on LAN Together with Manageability</li> <li>Spec Changes added:</li> <li>1. Update to PBA Number EEPROM Word Format</li> <li>Errata added:</li> <li>37. TimeSync: Missing Tx timestamps in SerDes mode</li> <li>38. Virtualization: Dropped Packets When Using VM-to-VM Switching</li> </ul>                                                                                                                       |

| September 9, 2010  | 2.73     | <ul> <li>Spec Clarification added:</li> <li>6. Critical Session (Keep PHY Link Up) Mode Does Not Block All PHY Resets Caused by PCIe Resets - Moved from Errata.</li> <li>Spec Change, language updated:</li> <li>1. Update to PBA Number EEPROM Word Format Explanation expanded to address confusion about number format.</li> </ul>                                                                                                                                         |

| October 14, 2010   | 2.74     | Software Clarfication:<br>• 1. While In TCP Segmentation Offload, Each Buffer is Limited to 64 KB                                                                                                                                                                                                                                                                                                                                                                              |

| December 15, 2010  | 2.75     | Spec Clarification added:         • 7. SerDes: AN_TIMEOUT Only Works When Link Partner Idle         Errata added:         • 39. I2C Data Out Hold Time Violation                                                                                                                                                                                                                                                                                                               |

| April 20, 2011     | 2.76     | <ul> <li>Spec Changes added:</li> <li>2. PCIe: Device Control 2 Register Should Not Be Written While DMA Is Enabled</li> <li>3. Updates to PXE/iSCSI EEPROM Words</li> <li>Errata added:</li> <li>40. TSYNC: Auxiliary Timestamp from SDP is Unreliable</li> </ul>                                                                                                                                                                                                             |

| May 5, 2011        | 2.77     | <ul> <li>Spec Change added:</li> <li>4. Updated Definition of SW EEPROM Port Identification LED Blinking (Word 0x4)</li> </ul>                                                                                                                                                                                                                                                                                                                                                 |

| July 20, 2011      | 2.78     | Spec Changes added:         • 5. SerDes Forced Mode Override EEPROM Setting         • 6. Update to the Sequence in Switching Between Media         Errata added:         • 41. NC-SI: Get Link Status Command Might Cause Corruption of PHY Registers                                                                                                                                                                                                                          |

| August 2, 2011     | 2.79     | Software Clarification added:<br>• 2. Serial Interfaces Programmed By Bit Banging                                                                                                                                                                                                                                                                                                                                                                                              |

| September 14, 2011 | 2.80     | Errata added:<br>• 42. NC-SI: Get NC-SI Pass-through Statistics Response Format                                                                                                                                                                                                                                                                                                                                                                                                |

| November 28, 2011  | 2.81     | <ul> <li>Table 1, Product Identification and Packaging is an update. It replaces two older tables. Introduces the A2 stepping. A2 is functionally the same as A1.</li> <li>Errata added:</li> <li>43. PCIe: Receiver Overflow Error .</li> </ul>                                                                                                                                                                                                                               |

| December 7, 2011   | 2.82     | <ul> <li>Added A2 information to status data for each errata.</li> <li>Added the following text in Section 1.20: "There is an internal designator visible as a dash on the die side of some packages. It's location may differ. The mark (looks like a dash, approximately 300X1000 µm in size) does not impact function."</li> </ul>                                                                                                                                          |

| December 13, 2011  | 2.83     | • Table 1, Product Identification and Packaging. A table note has been updated.<br>The new text is: "There is no die change for parts listed as A2. There are no<br>Form, Fit, or Function changes to this silicon. Intel anticipates no impact to<br>customers. This is an internal package change to provide a material solution<br>that is RoHS compliant; Intel qualified and certified this change in the same<br>way as it does for all products supplied to customers." |

| Date              | Revision | Description                                                                                                                                                                                  |  |  |

|-------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| January 30, 2012  | 2.84     | Spec Clarifications added:<br>• 8. Padding on Transmitted SCTP Packets                                                                                                                       |  |  |

| September 4, 2012 | 2.85     | <ul> <li>Spec Clarification:         <ul> <li>9. Dynamic LED Modes Can Only Be Used in an Active Low Configuration</li> <li>Spec Change added:                 <ul></ul></li></ul></li></ul> |  |  |

Revisions - Intel<sup>®</sup> 82576EB GbE Controller

NOTE: This page intentionally left blank.

# 1.10 Introduction

This document applies to the 82576.

This document is an update to a published specification, the *Intel<sup>®</sup> 82576EB Gigabit Ethernet Controller Datasheet*. It is intended for use by system manufacturers and software developers. All product documents are subject to frequent revision and new order numbers may apply. New documents may be added. Be sure you have the latest information before finalizing your design.

References to PCIe\* in this document refer to PCIe v2.0 (2.5GT/s).

# 1.20 Product Code and Device Identification

The following table describes identication and packaging information.

| Lead (Pb) |         |                                     |  |        |                           |         |  |        |  |

|-----------|---------|-------------------------------------|--|--------|---------------------------|---------|--|--------|--|

| Device    | Step*   | Top<br>Marking<br>[Product<br>Code] |  | Spec   | Description               | Media** |  | MM#    |  |

| 82576EB   | A2*     | HL82576EB                           |  | S LJBC | PRODUCTION                | T&R**   |  | 916949 |  |

| 82576EB   | A2      | HL82576EB                           |  | S LJBD | PRODUCTION                | TRAY    |  | 916950 |  |

| 82576EB   | A2      | HL82576EB                           |  | Q PE4  | ENGINEERING               | TRAY    |  | 916530 |  |

| 82576EB   | A1      | HL82576EB                           |  |        | PRODUCTION                | TRAY    |  | 898304 |  |

| 82576EB   | A1      | HL82576EB                           |  |        | PRODUCTION                | T&R     |  | 898303 |  |

| Device    | Pb) Fre | Top<br>Marking<br>[Product<br>Code] |  | Spec*  | Description               | Media** |  | MM#    |  |

| 82576EB   | A2*     | JL82576EB                           |  | S LJBG | PRODUCTION                | T&R**   |  | 916955 |  |

| 82576EB   | A2      | JL82576EB                           |  | S LJBH | PRODUCTION                | TRAY    |  | 916956 |  |

| 82576EB   | A2      | JL82576GB                           |  | S LJBL | PRODUCTION                | T&R     |  | 916959 |  |

| 82576EB   | A2      | JL82576GB                           |  | S LJBM | PRODUCTION                | TRAY    |  | 916960 |  |

| 82576EB   | A2      | JL82576NS                           |  | S LJBN | PRODUCTION<br>NO SECURITY | T&R     |  | 916961 |  |

| 82576EB   | A2      | JL82576NS                           |  | S LJBP | PRODUCTION<br>NO SECURITY | TRAY    |  | 916962 |  |

# Table 1. Product Identification and Packaging

| 82576EB | A2 | JL82576EB | Q PE6 | ENGINEERING               | TRAY | 916652 |  |

|---------|----|-----------|-------|---------------------------|------|--------|--|

| 82576EB | A2 | JL82576GB | Q PE8 | ENGINEERING               | TRAY | 916654 |  |

| 82576EB | A2 | JL82576NS | Q PE9 | ENGINEERING               | TRAY | 916655 |  |

| 82576EB | A1 | JL82576EB |       | PRODUCTION                | TRAY | 897983 |  |

| 82576EB | A1 | JL82576EB |       | PRODUCTION                | T&R  | 897979 |  |

| 82576EB | A1 | JL82576NS |       | PRODUCTION<br>NO SECURITY | TRAY | 899826 |  |

| 82576EB | A1 | JL82576NS |       | PRODUCTION<br>NO SECURITY | T&R  | 899825 |  |

# Table 1. Product Identification and Packaging (Continued)

\* There is no die change for parts listed as A2. There are no Form, Fit, or Function changes to this silicon. Intel anticipates no impact to customers. This is an internal package change to provide a material solution that is RoHS compliant; Intel qualified and certified this change in the same way as it does for all products supplied to customers. \*\* Tray or T&R (Tape and reel).

.,....,

# Table 2. Device ID

| 82576 Device ID Code                     | Vendor ID | Device ID | Revision ID* |

|------------------------------------------|-----------|-----------|--------------|

| 82576 (Copper Applications)              | 0x8086    | 0x10C9    | 1            |

| 82576 (Fiber Applications)               | 0x8086    | 0x10E6    | 1            |

| 82576 (SerDes Backplane Applications)    | 0x8086    | 0x10E7    | 1            |

| 82576 (Non-Security Copper Applications) | 0x8086    | 0x150A    | 1            |

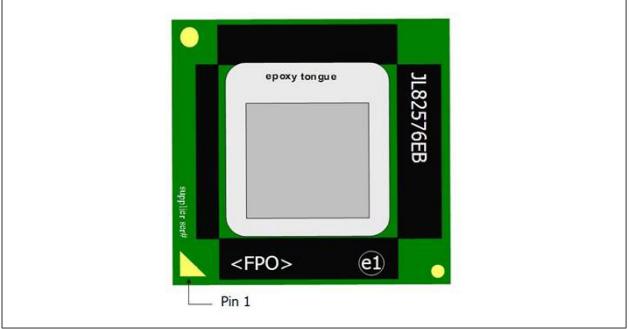

# 1.30 Marking Diagram

# Figure 1. Example With Identifying Marks

Lead-free parts will have "JL" as the prefix for the product code (vs. "HL").

The devices can also have a "GB" marking, instead of "EB". These are functionally equivalent and only used on Intel network interface adapters.

There is an internal designator visible as a dash on the die side of some packages. It's location may differ. The mark (looks like a dash, approximately  $300 \times 1000 \ \mu m$  in size) does not impact function.

# 1.40 Nomenclature Used In This Document

This document uses specific terms, codes, and abbreviations to describe changes, errata, sightings and/or clarifications that apply to silicon/steppings. See Table 3 for a description.

| Name                            | Description                                                                                                                                                                                                                                                                                                                |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Specification<br>Changes        | Modifications to the current published specifications. These changes will be incorporated in the next release of the specifications.                                                                                                                                                                                       |

| Errata                          | Design defects or errors. Errata may cause device behavior to deviate from published specifications.<br>Hardware and software designed to be used with any given stepping must assume that all errata documented<br>for that stepping are present on all devices.                                                          |

| Sightings                       | Observed issues that are believed to be errata, but have not been completely confirmed or root caused. The intention of documenting sightings is to proactively inform users of behaviors or issues that have been observed. Sightings may evolve to errata or may be removed as non-issues after investigation completes. |

| Specification<br>Clarifications | Greater detail or further highlights concerning a specification's impact to a complex design situation. These clarifications will be incorporated in the next release of the specifications.                                                                                                                               |

| Documentation<br>Changes        | Typos, errors, or omissions from the current published specifications. These changes will be incorporated in the next release of the specifications.                                                                                                                                                                       |

| A1, B1, etc.                    | Stepping to which the status applies.                                                                                                                                                                                                                                                                                      |

| Doc                             | Document change or update that will be implemented.                                                                                                                                                                                                                                                                        |

| Fix                             | This erratum is intended to be fixed in a future stepping of the component.                                                                                                                                                                                                                                                |

| Fixed                           | This erratum has been previously fixed.                                                                                                                                                                                                                                                                                    |

| EEPROM/NVM Fix                  | This indicates the Errata was in the EEPROM/NVM and is fixed in an updated version.                                                                                                                                                                                                                                        |

| NoFix                           | There are no plans to fix this erratum.                                                                                                                                                                                                                                                                                    |

| Eval                            | Plans to fix this erratum are under evaluation.                                                                                                                                                                                                                                                                            |

| Red Change Bar/<br>or Bold      | This Item is either new or modified from the previous version of the document.                                                                                                                                                                                                                                             |

# Table 3. Nomenclature

# 1.50 Sightings, Clarifications, Changes, Errata and Software Clarifications

See Section 1.40 for an explanation of terms, codes, and abbreviations.

# Table 4. Summary of Sightings, Clarifications, Changes, Errata, Software Clarifications; Errata Include Steppings

| Sightings                                                            | Status |

|----------------------------------------------------------------------|--------|

| None.                                                                | NA     |

| Specification Clarifications                                         | Status |

| 1. PCIe: End Point Request of I/O Space After Initialization         | NA     |

| 2. PCIe: Partial Memory-Write Requests Actually Writing Full DW      | NA     |

| 3. PCIe: Completion Timeout Mechanism Compliance                     | NA     |

| 4. PCIe: Receiver Dtection Circuit Design and Established Link Width | NA     |

# Table 4. Summary of Sightings, Clarifications, Changes, Errata, Software Clarifications; Errata Include Steppings (Continued)

| 5. Use of Wake on LAN Together with Manageability                                                                            | NA           |

|------------------------------------------------------------------------------------------------------------------------------|--------------|

| 6. Critical Session (Keep PHY Link Up) Mode Does Not Block All PHY Resets Caused by PCIe<br>Resets                           | NA           |

| 7. SerDes: AN_TIMEOUT Only Works When Link Partner Idle                                                                      | NA           |

| 8. Padding on Transmitted SCTP Packets                                                                                       | NA           |

| 9. Dynamic LED Modes Can Only Be Used in an Active Low Configuration                                                         | NA           |

| Specification Changes                                                                                                        | Status       |

| 1. Update to PBA Number EEPROM Word Format                                                                                   | NA           |

| 2. PCIe: Device Control 2 Register Should Not Be Written While DMA Is Enabled                                                | NA           |

| 3. Updates to PXE/iSCSI EEPROM Words                                                                                         | NA           |

| 4. Updated Definition of SW EEPROM Port Identification LED Blinking (Word 0x4)                                               | NA           |

| 5. SerDes Forced Mode Override EEPROM Setting                                                                                | NA           |

| 6. Update to the Sequence in Switching Between Media                                                                         | NA           |

| 7. CRC8 Fields of Analog Initialization Structures in the EEPROM Image are not Checked by the Device                         | NA           |

| Errata                                                                                                                       | Status       |

| 1. Internal Copper PHY: Improperly Implements Auto-Negotiation Advertisement Register                                        | A1, A2 NoFix |

| 2. PCIe: Differential Return Loss More than Specified Value                                                                  | A1, A2 NoFix |

| 3. SGMII Counters Incorrectly Increment on Collision                                                                         | A1, A2 NoFix |

| 4. Internal Copper PHY: Test Equipment May Report Master/Slave Device Doesn't Correctly<br>Implement Master/Slave Resolution | A1, A2 NoFix |

| 5. Internal Copper PHY: Auto-MDX Improperly Implements Sample Timer                                                          | A1, A2 NoFix |

| 6. SCTP CRC Check Incorrect                                                                                                  | A1, A2 NoFix |

| 7. TLP: Poisoned TLP Reported In All Functions Instead Of Only Target                                                        | A1, A2 NoFix |

| 8. Internal Copper PHY: 10BASE-T IDL Template Failure                                                                        | A1, A2 NoFix |

| 9. Internal Copper PHY: 10BASE-T Link Pulse Hits Template Mask Due To Voltage Ripple/Glitch                                  | A1, A2 NoFix |

| 10. MAC: Wakeup Event Occurs On Magic Packet That Doesn't Pass Address Filter                                                | A1, A2 NoFix |

| 11. PCIe: L0s Exit Latency In Link Capabilities Register Not Updated For Common Clock Configuration                          | A1, A2 NoFix |

| 12. Time SYNC: Reserved Bits Must Be Zero In PTP Header                                                                      | A1, A2 NoFix |

| 13. Internal Copper PHY: No Link In Forced Mode                                                                              | A1, A2 NoFix |

| 14. Duplicate. See 18.                                                                                                       |              |

# Table 4. Summary of Sightings, Clarifications, Changes, Errata, Software Clarifications; Errata Include Steppings (Continued)

| 15. Internal Copper PHY: IEEE 1411.10.03 – 10BASE-T Harmonic Content Fails at Low Voltage                           | A1, A2 NoFix       |

|---------------------------------------------------------------------------------------------------------------------|--------------------|

| 16. NC-SI: Additional Multicast Packets May Be Forwarded To MC                                                      | A1, A2 NoFix       |

| 17. SMBus: Unread Packets Received On One Port May Cause Loss of Ability To Receive on<br>Other Port                | A1, A2 NoFix       |

| 18. JTAG: Instruction Register Functionality Doesn't Meet IEEE Std 1149-1-2001                                      | A1, A2 NoFix       |

| 19. LED Stays On When SerDes Is Powered Down                                                                        | A1, A2 NoFix       |

| 20. PCIe Elastic Buffer Noise Immunity Is Not Optimized                                                             | Fixed.             |

| 21. PCIe: Missing Replay Due to Recovery During TLP Transmission                                                    | A1, A2 NoFix       |

| 22. PCIe: LTSSM Moves from L0 to Recovery Only When Receiving TS1/TS2 on All Lanes                                  | A1, A2 NoFix       |

| 23. This entry moved from the Errata to Specification Clarification section (above).                                | N/A                |

| 24. PCIe: Missing Completion on D3 to D0 Transition                                                                 | A1, A2 NoFix       |

| 25. PCIe: Completion Timeout Settings Not Loaded from EEPROM to GCR                                                 | A1, A2 NoFix       |

| 26. MSI-X: Descriptor Write-back Not Triggered by EITR Expiration in MSI-X Mode                                     | A1, A2 NoFix       |

| 27. Tx Packet Lost After PHY Speed Change Using Auto-Negotiation                                                    | A1, A2 NoFix       |

| 28. PCIe: Wrong Byte Enable Bit Used for Completion Timeout Disable Bit in Device Control 2<br>Register             | A1, A2 NoFix       |

| 29. PCIe: Completion with UR/CA Status Causes Unexpected Completion and Completion<br>Timeout Errors to be Reported | A1, A2 NoFix       |

| 30. PCIe Hot Reset Can Lead to a Firmware Hang                                                                      | A1, A2 NoFix       |

| 31. MACSec: Replay Protect Not Working In Check Mode                                                                | A1, A2 NoFix       |

| 32. MACSec: Packets With E=0, C=1 Should Not Be Handled as a Authenticated MACSec<br>Packet                         | A1, A2 NoFix       |

| 33. MACSec: Packets With PN = 0 In The SECTAG Are Not Dropped                                                       | A1, A2 NoFix       |

| 34. MACSec: SA Creation Doesn't Clear Frame Verification Statistics                                                 | A1, A2 NoFix       |

| 35. MACSec: LSECRXNUSA and LSECRXUNSA Statistic Counters Not Provided                                               | A1, A2 NoFix       |

| 36. MACSec: When MC Is MACSec owner, MAC Reset Still Clears Keys                                                    | A1, A2 NoFix       |

| 37. TimeSync: Missing Tx timestamps in SerDes mode                                                                  | A1, A2 NoFix       |

| 38. Virtualization: Dropped Packets When Using VM-to-VM Switching                                                   | A1, A2 NoFix       |

| 39. I2C Data Out Hold Time Violation                                                                                | A1, A2 NoFix       |

| 40. TSYNC: Auxiliary Timestamp from SDP is Unreliable                                                               | A1, A2 NoFix       |

| 41. NC-SI: Get Link Status Command Might Cause Corruption of PHY Registers                                          | A1, EEPROM/NVM Fix |

| 42. NC-SI: Get NC-SI Pass-through Statistics Response Format                                                        | A1, A2 NoFix       |

| 43. PCIe: Receiver Overflow Error                                                                                   | A1, A2 NoFix       |

# Table 4. Summary of Sightings, Clarifications, Changes, Errata, Software Clarifications; Errata Include Steppings (Continued)

| 44. PF's MSI TLP Might Contain the Wrong Requester ID When a VF Uses MSI-X | A1, A2 NoFix |

|----------------------------------------------------------------------------|--------------|

| Software Clarifications                                                    | Status       |

| 1. While In TCP Segmentation Offload, Each Buffer is Limited to 64 KB      | NA           |

| 2. Serial Interfaces Programmed By Bit Banging                             | NA           |

| 3. PF/VF Drivers Should Configure Registers That Are Not Reset By VFLR     | NA           |

# 1.5.1 Sightings

None.

# 1.5.2 **Specification Clarifications**

# 1. PCIe: End Point Request of I/O Space After Initialization

Clarification: The 82576 requests I/O space if EEPROM bit 14, word 0x19 is set. When this EEPROM bit is set, I/O Space is always requested.

The specification does not define a way to signal that IO BAR usage is done. When PCIe compliance tests are run, this may cause a test failure.

Failure when running PCI SIG compliance tests with EEPROM bit 14, word 0x19 set.

- Workaround: Disable I/O BAR requests via EEPROM bit 14, word 0x19. Since various pre-boot SW tools require the I/O Space be requested, the bit is enabled by default in EEPROM images.

- ▼ Return to Summary

# 2. PCIe: Partial Memory-Write Requests Actually Writing Full DW

Clarification: The PCIe specification allows a device not to accept certain requests. This is under "programming model" cases. The device needs to issue a Completer Abort error if specific request violates the programming model. As part of its programming model, the 82576 does not support writes and reads with Byte Enables to specific memory addresses. Such writes will be fully executed and will not be treated as completion abort.

CSR writes and reads with partial (or zero) Byte Enables will be executed (in specific address ranges). This scenario will not happen when using the device driver and this functionality is also not needed for the normal operation of the design.

Workaround: No partial (zero) Byte Enables writing and reading to the device.

▼ Return to Summary

## 3. PCIe: Completion Timeout Mechanism Compliance

Clarification: PCIe Completion Timeout value must be properly set.

The 82576 Completion Timeout Value(3:0) must be properly set by the system BIOS in Intel PCIe Configuration Space Device Control 2 Register (0xC8; RW). Failure to do so can cause unpredictable system behavior.

The 82576 complies with the PCIe 2.0 Specification for the completion timeout mechanism and programmable timeout values. The PCIe 2.0 Specification provides programmable timeout ranges between 50us to 64s with a default time range of 50us-50ms. The 82576 defaults to a range of 500us – 1ms for PCIe capabilities version 1 and 2. The PCIe 2.0 Specification also strongly recommends that the default timeout value be such that the completion timeout mechanism not expire in less than 10ms.

The completion timeout value must be programmed correctly in PCIe configuration space (in Device Control 2 Register); the value must be set above the expected maximum latency for completions in the system in which the 82576 is installed. This will ensure that the 82576 receives the completions for the requests it sends out, avoiding a completion timeout scenario. Failure to properly set the completion timeout value can result in the device timing out prior to a completion returning. In the event of a completion timeout, the device assumes the original completion is lost, and resends the original request, by default. In this condition, if the completion for the original request arrives at the 82576 device, this will result in 2 completions arriving for the same request, which may cause unpredictable system behavior.

As long as the Completion Timeout value is properly programmed by the system the completion timeout mechanism works without issue. It is expected that the system BIOS will set this value appropriately for the system.

Workaround: Alternatively a device driver could ensure the completion timeout value is set above 10ms (in order to follow the recommendation of the PCIe 2.0 specification). The driver would modify the timeout value, if and only if the default timeout value remains in configuration space. This will not impact BIOSs already changing the timeout value since the driver will not override any non-default setting of the timeout value. For extra protection against unpredictable system behavior in case the timeout setting is incorrect, it is recommended to disable the resend of the request. This can be done by clearing the Completion\_Timeout\_Resend bit in the GCR Register.

The latest Intel drivers implement this workaround by modifying the completion timeout value in config space if the timeout value is still set to a value of 0x0 when the driver loads. They also clear the Completion\_Timeout\_Resend bit in the GCR Register.

## Release 14.4 includes this fix.

▼ Return to Summary

## 4. PCIe: Receiver Dtection Circuit Design and Established Link Width

Clarification: The 82576 receiver detection circuit was designed according to the PCIe Specification Rev. 1.1, which requires that an un-terminated receiver have an input impedance of at least 200 Kohm. PCIe Specification Rev. 2.0 allows the input impedance to be as low as 1 Kohm at input voltages in the range -150 - 0 mV and does not specify a minimum input impedance below -150 mV. As a result, a powered-down receiver lane with low input impedance at negative voltages could be compliant to Rev 2.0 and yet be falsely detected by the 82576 as a terminated lane.

This is normally not an issue since any connnected lanes should be properly terminated within 5 ms after fundamental reset according to the PCIe Specification. However, there are some chipset devices that require significantly more time to prepare the termination and expect the link partner to remain in the LTSSM Detect state as long as none of the lanes are terminated. When used with such devices, the 82576 might falsely detect a receiver on one or more lanes and leave the Detect state. This can lead to establishing a link that is less than full width.

In this case, it is recommended that a Hot Reset be performed after a link has been established in order to force the 82576 to detect the receivers again when they are properly terminated. As a result, a full-width link can be established.

Workaround: Not Applicable.

#### **V** Return to Summary

## 5. Use of Wake on LAN Together with Manageability

Clarification: The Wakeup Filter Control Register (WUFC) contains the NoTCO bit, which affects the behavior of the wakeup functionality when manageability is in use. Note that if manageability is not enabled, the value of NoTCO has no effect.

When NoTCO contains the hardware default value of 0b, any received packet that matches the wakeup filters will wake the system. This could cause unintended wakeups in certain situations. For example, if Directed Exact Wakeup is used and the manageability shares the host's MAC address, IPMI packets that are intended for the BMC wake the system, which might not be the intended behavior.

When NoTCO is set to 1b, any packet that passes the manageability filter, even if it also is copied to the host, is excluded from the wakeup logic. This solves the previous problem since IPMI packets do not wake the system. However, with NoTCO=1b, broadcast packets, including broadcast magic packets, do not wake the system since they pass the manageability filters and are therefore excluded.

## Table 5. Effects of NoTCO

| WoL Type       | ΝοΤCΟ | Shared MAC<br>Address | Unicast Packet                                                            | Broadcast Packet |

|----------------|-------|-----------------------|---------------------------------------------------------------------------|------------------|

| Magic Packet   | Ob    | -                     | ОК                                                                        | ОК               |

| Magic Packet   | 1b    | Y                     | No wake                                                                   | No wake          |

| Magic Packet   | 1b    | Ν                     | ОК                                                                        | No wake          |

| Directed Exact | Ob    | Y                     | Wake even if MNG packet. No<br>way to talk to BMC without<br>waking host. | N/A              |

| Directed Exact | Ob    | Ν                     | ОК                                                                        | N/A              |

| Directed Exact | 1b    | -                     | ОК                                                                        | N/A              |

The Intel Windows\* drivers set NoTCO by default.

If this is not the desired behavior, the EnableWakeOnManagmentOnTCO registry entry can be used to change it starting with Intel LAN driver software release 15.5. Setting this registry entry to 1b causes the driver to program NoTCO to 0b. A tool to modify the registry entry can be provided.

Contact your Intel representative for access.

Workaround: N/A.

## ▼ Return to Summary

## 6. Critical Session (Keep PHY Link Up) Mode Does Not Block All PHY Resets Caused by PCIe Resets

- Clarification: D3 to D0 transition will cause a PHY reset even in Keep PHY Link Up mode. When Critical Session Mode (Keep PHY Link Up) is enabled (via the NC-SI Set Intel Management Control command or the SMBUS Management Control command), PCIe resets should not cause a PHY reset. However, the following events will still cause a PHY reset:

- Transition from D3 to D0 without general PCIe reset (i.e. PMCSR[1:0] changed from 11 to 00 by configuration write)

- Function-level reset

Implication: Loss of link can cause a loss of the MNG session. These events do not normally occur during a reboot cycle, so it is expected that no effect will be seen in most circumstances.

# Workaround: N/A.

▼ Return to Summary

# 7. SerDes: AN\_TIMEOUT Only Works When Link Partner Idle

Clarification: The auto-negotiation timeout mechanism (PCS\_LCTL.AN\_TIMEOUT\_EN) only works if the SerDes partner is sending idle code groups continuously for the duration of the timeout period, which is the usual case. However, if the partner is transmitting packets, an autonegotiation timeout will not occur since auto-negotiation is restarted at the beginning of each packet.

> If the partner has an application that indefinitely transmits data despite the lack of any response, it is possible that a link will not be established. If this is a concern, the autonegotiation timeout mechanism may be considered unreliable and an additional software mechanism could be used to disable auto-negotiation if sync is maintained without a link being established (PCS\_LSTS.SYNC\_OK=1b and PCS\_LSTS.LINK\_OK=0b) for an extended period of time.

Note: To Disable Auto-Negotiation when using an Intel driver, use the SerDes Forced Mode Override bit as described in Specification Change #5.

Workaround: N/A

- ▼ *Return to Summary*

- 8. Padding on Transmitted SCTP Packets

- Clarification: When using the 82576 to offload the CRC calculation for transmitted SCTP packets, software should not add Ethernet padding bytes to short packets (less than 64 bytes). Instead, the TCTL.PSP bit should be set so that the 82576 pads the packets after performing the CRC calculation.

Workaround: N/A

**V** Return to Summary

#### 9. Dynamic LED Modes Can Only Be Used in an Active Low Configuration

Clarification: In any of the dynamic LED modes (FILTER\_ACTIVITY, LINK/ACTIVITY, COLLISION, ACTIVITY, PAUSED), LED blinking should only be enabled if the LED signal is configured as an active low output.

Workaround: N/A

▼ Return to Summary

# 1.5.3 Specification Changes

## 1. Update to PBA Number EEPROM Word Format

Change: PBA Number Module — Word 0x8-0x9

The nine-digit Printed Board Assembly (PBA) number used for Intel manufactured Network Interface Cards (NICs) is stored in EEPROM.

Through the course of hardware ECOs, the suffix field is incremented. The purpose of this information is to enable customer support (or any user) to identify the revision level of a product.

Network driver software should not rely on this field to identify the product or its capabilities.

PBA numbers have exceeded the length that can be stored as HEX values in two words. For newer NICs, the high word in the PBA Number Module is a flag (0xFAFA) indicating that the actual PBA is stored in a separate PBA block. The low word is a pointer to the starting word of the PBA block.

The following shows the format of the PBA Number Module field for new products.

| PBA Number | Word 0x8 | Word 0x9             |

|------------|----------|----------------------|

| G23456-003 | FAFA     | Pointer to PBA Block |

The following provides the format of the PBA block; pointed to by word 0x9 above:

| Word Offset | Description                                       |

|-------------|---------------------------------------------------|

| 0x0         | Length in words of the PBA Block (default is 0x6) |

| 0x1 0x5     | PBA Number stored in hexadecimal ASCII values.    |

The new PBA block contains the complete PBA number and includes the dash and the first digit of the 3-digit suffix which were not included previously. Each digit is represented by its hexadecimal-ASCII values.

The following shows an example PBA number (in the new style):

| PBA Number | Word<br>Offset 0     | Word<br>Offset 1 | Word<br>Offset 2 | Word<br>Offset 3 | Word<br>Offset 4 | Word<br>Offset 5 |

|------------|----------------------|------------------|------------------|------------------|------------------|------------------|

| G23456-003 | 0006                 | 4732             | 3334             | 3536             | 2D30             | 3033             |

|            | Specifies 6<br>words | G2               | 34               | 56               | -0               | 03               |

Older NICs have PBA numbers starting with [A,B,C,D,E] and are stored directly in words 0x8-0x9. The dash in the PBA number is not stored; nor is the first digit of the 3-digit suffix (the first digit is always 0b for older products).

The following example shows a PBA number stored in the PBA Number Module field (in the old style):

| PBA Number | Byte 1 | Byte 2 | Byte 3 | Byte 4 |

|------------|--------|--------|--------|--------|

| E23456-003 | E2     | 34     | 56     | 03     |

**V** Return to Summary

# 2. PCIe: Device Control 2 Register Should Not Be Written While DMA Is Enabled

- Change: The Device Control 2 Register should only be written during initialization. When a port is enabled to transmit or receive data, this register should not be written even if the value is not changed.

- ▼ Return to Summary

# 3. Updates to PXE/iSCSI EEPROM Words

Change: For Gigabit Main Setup Options Word 0x30, 0x34; bits 2:0 and bit 5 are now defined as indicated in the table below.

|        |                            | 1                                                                                                           | 1                      |                                                                                                                                  |                                                                                                         |  |  |

|--------|----------------------------|-------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|

| Bit(s) | Value                      | Port Status                                                                                                 | CLP(Combo)<br>Executes | iSCSI Boot Option ROM<br>CTRL-D Menu                                                                                             | FCoE Boot Option ROM<br>CTRL-D Menu                                                                     |  |  |

| 15:7   | Same as before. No change. |                                                                                                             |                        |                                                                                                                                  |                                                                                                         |  |  |

| 5      | Bit 5, forme               | Bit 5, formerly used to indicate iSCSI enable / disable, is no longer valid and is not checked by software. |                        |                                                                                                                                  |                                                                                                         |  |  |

| 4:3    | Same as be                 | e as before. No change.                                                                                     |                        |                                                                                                                                  |                                                                                                         |  |  |

|        | 5-7                        | Reserved.                                                                                                   | Same as Disabled.      |                                                                                                                                  |                                                                                                         |  |  |

|        | 4                          | FCoE                                                                                                        | FCOE                   | <ul> <li>Displays port as FCoE.</li> <li>Allows changing to port to<br/>Boot Disabled, iSCSI<br/>Primary or Secondary</li> </ul> | <ul> <li>Displays port as FCoE.</li> <li>Allows changing to Boot<br/>Disabled</li> </ul>                |  |  |

|        | 3                          | iSCSI<br>Secondary                                                                                          | iSCSI                  | <ul> <li>Displays port as iSCSI<br/>Secondary.</li> <li>Allows changing to Boot<br/>Disabled, iSCSI Primary</li> </ul>           | <ul> <li>Displays port as iSCSI.</li> <li>Allows changing to Boot<br/>Disabled, FCoE enabled</li> </ul> |  |  |

|        | 2                          | iSCSI<br>Primary                                                                                            | iSCSI                  | <ul> <li>Displays port as iSCSI<br/>Primary.</li> <li>Allows changing to Boot<br/>Disabled, iSCSI Secondary</li> </ul>           | <ul> <li>Displays port as iSCSI.</li> <li>Allows changing to Boot<br/>Disabled, FCoE enabled</li> </ul> |  |  |

|        | 1                          | Boot Disabled                                                                                               | NONE                   | <ul> <li>Displays port as Disabled.</li> <li>Allows changing to iSCSI<br/>Primary/Secondary</li> </ul>                           | <ul> <li>Displays port as Disabled.</li> <li>Allows changing to FCoE enabled</li> </ul>                 |  |  |

| 2:0    | 0                          | PXE                                                                                                         | PXE                    | <ul> <li>Displays port as PXE.</li> <li>Allows changing to Boot<br/>Disabled, iSCSI Primary or<br/>Secondary</li> </ul>          | <ul> <li>Displays port as PXE.</li> <li>Allows changing to Boot<br/>Disabled, FCoE enabled</li> </ul>   |  |  |

▼ Return to Summary

# 4. Updated Definition of SW EEPROM Port Identification LED Blinking (Word 0x4)

Change: Driver software provides a method to identify an external port on a system through a command that causes the LED's to blink. Based on the setting in word 0x4, the LEDs drivers should blink between STATE1 and STATE2 when a port identification command is issued.

When word 0x4 is equal to 0xFFFF or 0x0000, the blinking behavior reverts to a default.

See the following table.

| Bit   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | Control for LED 3<br>0000b or 1111b: Default LED Blinking operation is used.<br>0001b = Default in STATE1 + Default in STATE2.<br>0010b = Default in STATE1 + LED is ON in STATE2.<br>0011b = Default in STATE1 + LED is OFF in STATE2.<br>0100b = LED is ON in STATE1 + Default in STATE2.<br>0101b = LED is ON in STATE1 + LED is OFF in STATE2.<br>0110b = LED is ON in STATE1 + LED is OFF in STATE2.<br>0111b = LED is OFF in STATE1 + Default in STATE2.<br>0111b = LED is OFF in STATE1 + Default in STATE2.<br>1000b = LED is OFF in STATE1 + LED is ON in STATE2.<br>1001b = LED is OFF in STATE1 + LED is OFF in STATE2.<br>1001b = LED is OFF in STATE1 + LED is OFF in STATE2.<br>1001b = LED is OFF in STATE1 + LED is OFF in STATE2.<br>1001b = LED is OFF in STATE1 + LED is OFF in STATE2. |

| 11:8  | Control for LED 2 - same encoding as for LED 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7:4   | Control for LED 1 – same encoding as for LED 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3:0   | Control for LED 0 – same encoding as for LED 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

**V** Return to Summary

# 5. SerDes Forced Mode Override EEPROM Setting

Change: Bit 14 in EEPROM Compatibility Word 0x3 is no longer reserved and defined as follows:

| Bit | Name                           | Default | Description                                                                                                                                                            |

|-----|--------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | SerDes Forced<br>Mode Override | 0       | SerDes Forced Mode Enable:<br>0 = Normal operation Intel Driver will enable PCS_LCTL.AN_ENABLE<br>1 = Forced Mode enable. Intel Driver will not set PCS_LCTL.AN_ENABLE |

This bit is only used by Intel drivers starting with Intel LAN Driver Release 16.4. This bit is read by Intel driver to determine if the device should be operated in SerDes forced mode. When the 82576 is not in SerDes mode this bit has no effect. The recommended setting for this bit is 0.

Note: Use the SerDes Forced Mode Override bit to allow the driver to disable Auto-Negotiation, in order to work around the issue described in Specification Clarification #7.

Return to Summary

## 6. Update to the Sequence in Switching Between Media

This is an update to the "Transition to the SerDes/SGMII Mode" procedure in the Datasheet Search for the procedure in Chapter 3 (Section 3.5.8.2.1\*). Use the following updated steps.

- 1. Disable the receiver by clearing RCTL.RXEN.

- 2. Disable the transmitter by clearing TCTL.EN.

- 3. Ensure Smart Power Down is not enabled in the PHY. EEPROM word 0xF bit 1 or PHY register 25d bit 0.

- 4. Verify the 8276 has stopped processing outstanding cycles and is idle.

- 5. Set CTRL.SPEED=10, CTRL.FRCSPD=1, CTRL\_EXT.SPD\_BYPS=1.

- 6. Modify LINK mode to SerDes or SGMII by setting CTRL\_EXT.LINK\_MODE to 11b or 10b, respectively.

- 7. Delay a minimum of 10-20µs

- 8. Clear CTRL.FRCSPD, CTRL\_EXT.SPD\_BYPS

- 9. Set up the link as described in Section 4.6.7.3, MAC/SERDES Link Setup (CTRL\_EXT.LINK\_MODE = 11b)\* or Section 4.6.7.4, MAC/SGMII Link Setup (CTRL\_EXT.LINK\_MODE = 10b)\*.

- 10. Set up Tx and Rx queues and enable Tx and Rx processes.

\*Links can change in a specific Datasheet revision. Use the links provided by the revision you are using.

- ▼ Return to Summary

- 7. CRC8 Fields of Analog Initialization Structures in the EEPROM Image are not Checked by the Device

- Change: See the "SerDes/PHY/PCIe/PLL/CCM Initialization Structures" section in Chapter 6 of the Datasheet. This section describes analog initialization structures. The CRC8 fields of these structures are not checked by the device.

- The CRC\_DIS EEPROM bit (word 0x23, bit 6) must be set to 1b.

- ▼ Return to Summary

# 1.5.4 Errata

1. Internal Copper PHY: Improperly Implements Auto-Negotiation Advertisement Register

Problem: The 82576 incorrectly transmits the link code word due to a write to register 4.

Implication: See the following notes on link code word bits:

Bits 4.7 and 4.8: Are always set in the base page transmission.

Bit 4.9: Represents 100BASE-T4 support. The 82576 does not support T4. It is unlikely that the auto-negotiation feature of the 82576 will be used in an implementation to advertise the presence of a T4 physical device. Therefore, the fact that this device does not allow T4 to be advertised is not significant.

Bit 4.15: The 82576 always supports Next Page (regardless the value of bit 4.15). When bit 4.15 is set to "one," the 82576 requires Register 7 (AN Next Page Transmit Register) to be written to complete the Next Page Exchange. In this case, the 82576's Next Pages do not correspond to Register 7, but contain valid 1000BASE-T Next Pages.

Workaround: Any write to register 4 should be followed with a restart of Auto-Negotiation by setting bit 0.9.

Status: A1, A2 NoFix

▼ Return to Summary

# 2. PCIe: Differential Return Loss More than Specified Value

Problem: The PCIe transmitter's differential return loss is -9.7 dB instead of the -10 dB requirement.

Implication: The out-of-specification return loss adds noise to the Tx line. Performance is not affected. Workaround: None.

Status: A1, A2 NoFix

▼ Return to Summary

# 3. SGMII Counters Incorrectly Increment on Collision

Problem: In SGMII mode/half duplex, the statistics counters listed below incorrectly increment when a collision occurs:

| Name    | Definition            | Location |

|---------|-----------------------|----------|

| RLEC    | Length error counter  | 0X4040   |

| CRCERRS | CRC error counter     | 0x4000   |

| RFC     | receive frame counter | 0x40A8   |

Implication: Error counters may not be accurate.

Workaround: None.

Status: A1, A2 NoFix

▼ Return to Summary

- 4. Internal Copper PHY: Test Equipment May Report Master/Slave Device Doesn't Correctly Implement Master/Slave Resolution

- Problem: When the internal Copper PHY is operating in 1000 Mbps forced slave mode, illegal data may be detected from the device during the transition from 10 Mbps mode (auto negotiation) to 1000 Mbps mode after master/slave resolution is complete.

- Implication: Test equipment checking for compliance of Master/Slave resolution may report failures when the device is in Force Slave mode. In Forced Slave mode, the device should not transmit any 1000 Mbps signals, which it is does not. However some test equipment looks for any activity sent from the device in forced slave mode and considers this a failure instead of looking for valid 1000 Mbps signals. Therefore, the illegal data may results in failures reported by test equipment.

Internal validation shows the device compiles with IEEE 802.3 Table 40-5; for all configurations, the device resolves to the correct defined mode

Workaround: None.

- Status: A1, A2 NoFix

- ▼ Return to Summary

## 5. Internal Copper PHY: Auto-MDX Improperly Implements Sample Timer

Problem: The Auto-Crossover State Machine (Auto-MDIX) has two states: MDI\_MODE and MDI- $X_MODE$ . The time that should be spent in each mode is defined as a multiple of a pseudo-random number and a sample timer, which is defined to be 62 ms ± 2 ms.

A violation occurs in  $\sim 10\%$  of the runs.

- Implication: The time that the PHY is in MDI mode will have a slight deviation from the specified definition.

- Workaround: None.

- Status: A1, A2 NoFix

- ▼ Return to Summary

## 6. SCTP CRC Check Incorrect

- Problem: For SCTP CRC check; if the SCTP packet is smaller than 64 bytes and padding is added, the SCTP CRC calculation is wrong.

- Implication: The 82576 could incorrectly indicate the SCTP CRC as incorrect.

- Workaround: If a 64-byte SCTP packet is received and the 82576 indicates the SCTP CRC is wrong (RDESC.ERRORS.L4E is set), the driver should re-calculate the CRC.

- Status: A1, A2 NoFix

- **V** Return to Summary

#### 7. TLP: Poisoned TLP Reported In All Functions Instead Of Only Target

Problem: A fatal message is incorrectly sent in response to a poisoned Transaction Layer Packet (TLP).

Implication: The 82576 treats all poisoned memory requests as non-function specific. Instead of reporting in the target function, a fatal error is reported in all functions.

The correct action is to report poisoned requests per function.

Workaround: None.

Status: A1, A2 NoFix

▼ Return to Summary

8. Internal Copper PHY: 10BASE-T IDL Template Failure

Problem: The 10BASE-T TP\_IDL waveform fails the template test on twisted-pair model combined with test load 2.

Implication: Specification violation. There is no impact on system level performance.

Workaround: None.

Status: A1, A2 NoFix

▼ Return to Summary

# 9. Internal Copper PHY: 10BASE-T Link Pulse Hits Template Mask Due To Voltage Ripple/Glitch

Problem: The 10BASE-T link pulse touches the specification template due to a voltage ripple/glitch.Implication: Specification violation. There is no effect at system level.Workaround: None.

Status: A1, A2 NoFix

▼ Return to Summary

# 10. MAC: Wakeup Event Occurs On Magic Packet That Doesn't Pass Address Filter